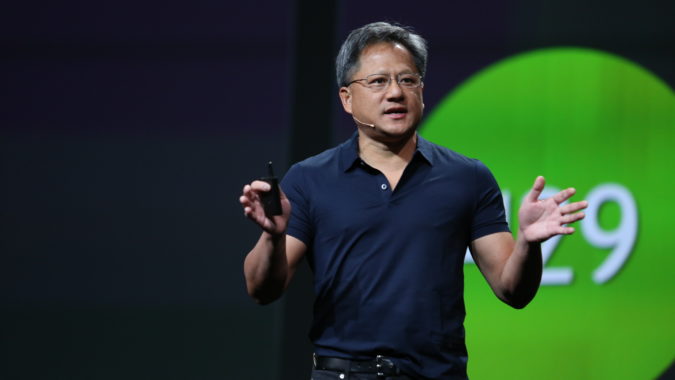

The GPU Technology Conference (GTC ’14) kicked off this morning in San Jose with NVIDIA CEO, Jen-Hsun Huang, opting to open the event with a preview of what’s ahead for GPUs in big data–and big computing. While the gaming and entertainment eye candy one expects at GTC did indeed find its way into the mix, high performance computing, machine learning, computer vision and large-scale analytics talk set the tone for the year, leaving no room for doubt that the GPU maker is serious about its business for performance and efficiency-conscious mainstream enterprise and research users.

NVIDIA’s roadmap for GPU computing revolves around resolving some of the core bottlenecks that have always existed for accelerators in terms of data movement and memory capability. In this era of “big data,” the performance levels drop off with the addition of ever-larger data streams, even with innovations that have tried to get around this by letting the GPU crunch while data movement goes on in the background as with recent efforts around direct memory access (DMA).

NVIDIA’s answer to the data movement bottleneck is found in today’s announcement of NVLink, which is its newly announced chip-to-chip communication approach that lets the GPU talk on a dedicated line with other GPUs, as well as hook directly to the CPU along unified memory lines without the weight of PCIe—which even at its best in the current 3.0 state can’t compare to what they’ve cooked. In effect, this bundle of PCIe pipes with DMA acts much like an extension of high bandwidth (and proprietary, one should add) PCIe. It splits the efficiency and performance drain of pure PCIe into components instead of running both through the same pipes. The end result, said Huang during his keynote, is a 5-12x performance improvement over PCIe 3.0 and a 4x efficiency boost.

NVIDIA was reluctant to share a great deal in the way of detail, but in essence, NVLink is comprised of bi-directional 8-lane “bricks” which can be put together to get the bandwidth boost promised. The speed on each of the lanes is around 20 Gb/s for each brick. However, it appears that this will be the second generation of the interconnect instead with the first iteration sporting a four-lane highway, which will be found first in Pascal, which we’ll get to in a moment.

In the event that a user is hooked in with a CPU that doesn’t support NVLink, the same fast lane can be opened between GPUs as below.

This is the sort of development one might expect out of a research group led by interconnect wizard, Bill Dally. And it might seem that there would have to be a “catch” of some sort. Other than having to start from the ground in terms of building and investing in new motherboards and an ecosystem, it’s hard to see what some of the challenges might be at this point beyond which OEMs will go out of their way to meet the terms of the yet-unannounced licensing plan. While it may involve a new set of motherboards to contend with, the good news is the module, which is very small, can be snapped in to allow for the construction of very dense servers. Additionally, the programming model shouldn’t be its own bottleneck as NVLink looks very mich like PCIe, but with its own special DMA capabilities to allow software to adapt to it easily. NVIDIA notes that the first generation will not be memory coherent, users will have to hold out for the second iteration of NVLink, by which time there might be a chance for an ecosystem to develop around it.

All of this work starts to hum together around the 2016 timeframe with the addition of Pascal, which was announced today to fill in the gaps between now and Volta. Pascal, named after the famous mathematician, will provide unified memory and 3D memory in addition to sporting what will likely be the first generation of NVLink. As you can see, the current status of Maxwell is right on time, however NVIDIA declined questions about when that would be extended to meet the needs of the Tesla group.

One of the key features of Pascal is the addition of stacked memory, which NVIDIA says will well over triple (almost quadruple) the bandwidth, from 288 to 1000 around a TB/sec. Additionally, this fix to the off-package GDDR5 is set to offer around 4x the energy efficiency by making the voltage regulators and compute close neighbors.

“GPUs have 288 GB/s of bandwidth already, which is many times that of the CPU—the very reason why GPUs contribute so much to parallel computation,” said Huang. “Of course we would love to have many times more. But the challenge is, the GPU already has a lot of pins; it’s already the biggest chip in the world. The interface is already very wide. How do you solve this when going wider would make the package enormous and making the signaling go faster would push down energy efficiency and we know we’re power limited in almost every application we’re pursing?”

During the keynote the emphasis was on various modes of mobility and access—from cloud-delivered services, self-driving cars with modular units in the trunk, hints at ultrasound and other medical devices being suitable hosts and more. In short, as we wait for NVIDIA to roll out Volta, Maxwell and eventually Pascal, could be making the rounds outside of the box.