After offering OpenPower Summit attendees a limited preview in April, IBM is unveiling further details of its next-gen CPU, Power9, which the tech mainstay is counting on to regain market share ceded to rival Intel. Built on GlobalFoundries 14nm finFET process technology, Power9 will be the centerpiece in Power-based servers starting in the second half of 2017. The highlight of the release is a brand new core and chip architecture that IBM has optimized for technical/HPC workloads, hyperscale, analytics and machine learning applications.

Although system availability hasn’t been announced yet, IBM has already landed a major win for its forthcoming Power9 platform. Back in November 2014, IBM, Mellanox and Nvidia were tapped to provide the DOE with two ~200-petaflops machines: Summit and Sierra. The $325 million contract specifies that the machines will employ Power9 CPUs and Volta GPUs when they come online next year.

IBM also has buy-in from Google, no small proof point in an era when hyperscalers exert substantial influence on the market. At the 2016 OpenPower Summit, Google said that the majority of its infrastructure had been ported to Power and that for most Googlers, enabling Power is a matter of a config change. Google is also working with Rackspace on a Power9 server, called Zaius, a design that will then be submitted to the Open Compute Project.

Without referencing specific customers or OpenPower partners, IBM indicated that chip-level derivatives based on Power9 could potentially be out in the 2018-2019 timeframe. A non-IBM Power8 chip was announced last year for the Chinese market. The CP1 was made by Suzhou PowerCore and was incorporated into Zoom Netcom’s RedPower C210 server.

Out of the gate, the Power9 family includes four different chip variations, targeting single and two-socket scale-out servers in commodity form factors and performance-optimized multi-socket scale-up servers. (IBM servers will start above $6,000, but other server manufacturers are free to offer lower-cost systems.) The scale out model will use direct attached memory with up to eight DDR4 ports, providing up to 120 GB/s of sustained bandwidth. The scale up designs use eight buffered channels, offering up to 230 GB/s of sustained bandwidth, and a greater number of SMP links to facilitate a larger SMP computer. The IBM Centaur memory buffer chips implemented in the scale-up models have L4 caches on board, providing low latency out of the L4 cache.

“It’s a tradeoff for the two different kinds of systems,” said Bill Starke, IBM distinguished engineer, Power Systems Memory Hierarchy and SMP Architecture at IBM. “With the scale-up you really get that extreme capacity up to practically 8 TB per socket and the strongest memory bandwidth – and back on the scale-out getting nice low latency, strong bandwidth across eight channels of DDR4 and of course getting the nice packaging solution of having the direct-attached memory.”

For both the scale-up and scale-out models, there are 24-core and 12-core variants.

“We either have 24 SMT4 cores or 12 SMT8 cores,” said Brian Thompto, senior technical staff member for POWER Processor Design at IBM, “our reasoning here was we wanted to hit all of the different customer optimization points – we wanted the 24 cores for good core-level virtualization granularity for the scale-out ecosystem datacenter space, the cloud space, and we wanted the 12 really strong SMT8 cores to provide larger partitions that fit very well with our customer needs for AIX and IPMI workloads running a type of RVM.”

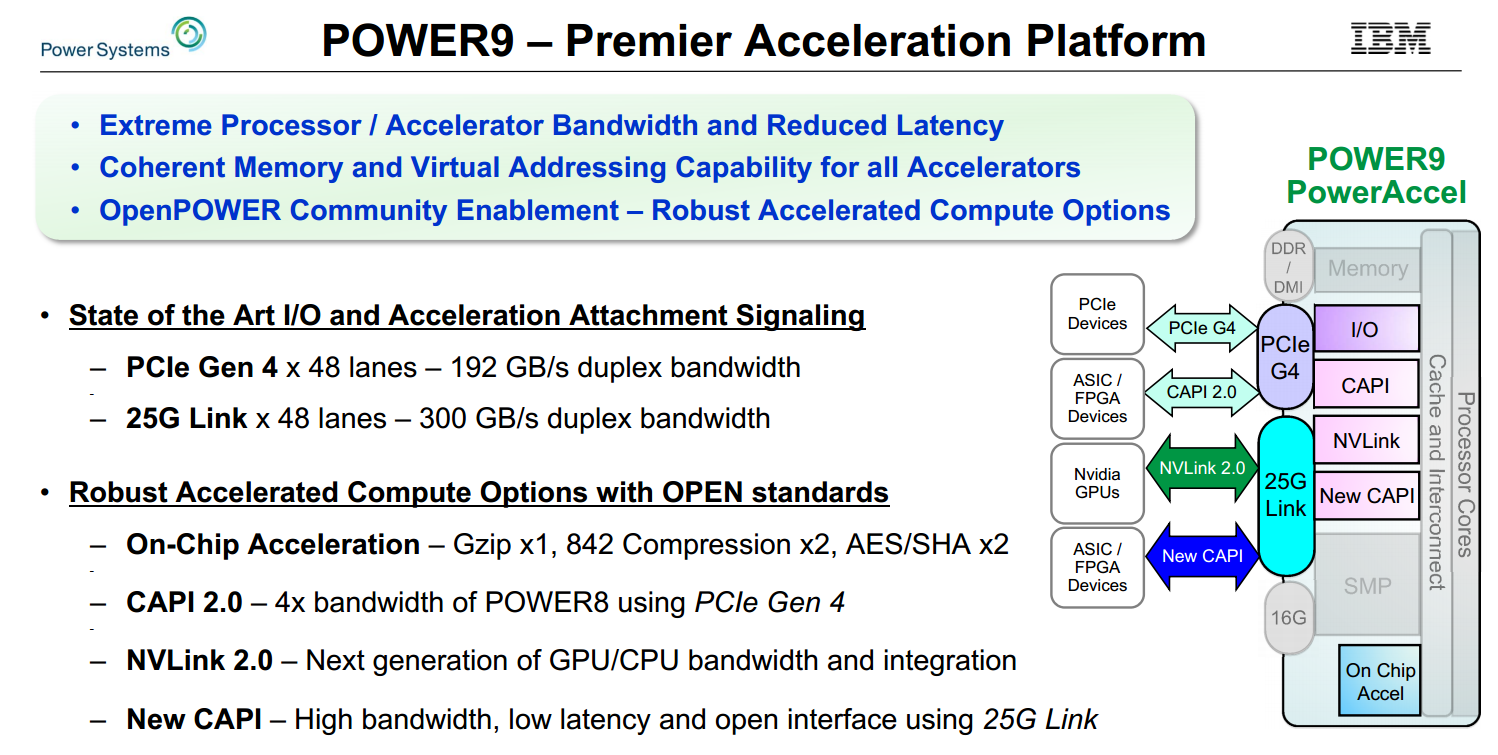

In keeping with its mission to enable accelerated and heterogeneous compute solutions, Power9 also includes some new signaling capabilities and protocols that bring the CPU and various accelerators closer together with access to memory.

“The acceleration capabilities that we are introducing they are not only enabling very strong CPU-GPU interaction and coupling; in addition to that they’re enabling a broad range of accelerators for highly-differentiated heterogeneous compute solutions,” said Thompto.

The above slide from IBM depicts how the Power9 CPU enables connectivity to a range of accelerators – Nvidia GPUs, ASICs, FPGAs, and PCIe-connected devices — using an array of interfaces. In addition to supporting PCIe Gen4, the CPU will employ NVLink 2.0, CAPI 2.0, and the successor to CAPI 2.0, currently being called New CAPI, ahead of an official naming.

“With CAPI 2.0 [over PCIe Gen4 x48 lanes], we not only run it over pins that run twice as fast but also run it over twice as many signals so you get an overall 4x bandwidth increase for that attach,” said Starke.

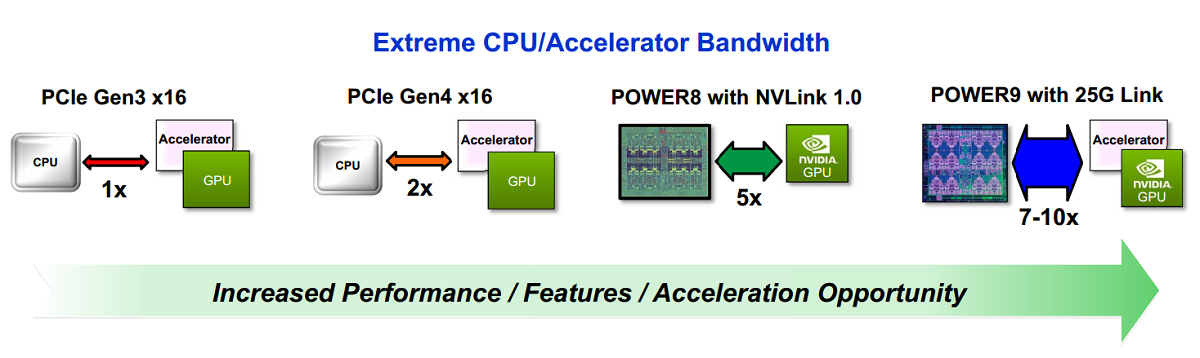

He added that IBM wasn’t content to stop at PCIe industry-standard protocols, hence the decision to implement a 48-lane 25 Gb/s accelerator-attach bus to further boost bandwidth and lower latency. The 25 Gb/s interconnect will power NVLink 2.0 as well as New CAPI, and will provide 300 Gb/s duplex bandwidth, said to be a 7x-10x improvement over PCIe Gen3 x16.

With its latest microarchitecture, IBM is reporting improved efficiency of its processor pipeline. Said Thompto, “The new design shortens fetch to compute by five cycles and if you look at completion — when we’re able to retire instructions — our fixed point total pipe from fetch to complete reduced by a similar number of cycles, five, and floating point actually reduced by eight cycles so we keep the instructions resident in the pipe less long, we’re able to better utilize our pipe and we get a lot of efficiency out of this as well.”

The Power9 family of chips are the first to implement the Power ISA 3.0, released by the OpenPower foundation. Notably the silicon has support for 128-bit IEEE 754 Quad-Precision Float, which will give IBM the distinction of having the first quadruple-precision hardware implementation. Each SMT4 processor has a full 128-bit quad-precision floating point precision engine, while each SMT8 processor has two of these engines since they are supporting twice as many threads. The wider precision will be a boon for certain financial and security workloads.

The Power9 chips also support half-precision float conversion, optimized for accelerator bandwidth and data exchange. IBM doesn’t see the need to implement half-precision floating point computation, a la Nvidia’s Pascal architecture and (likely) the forthcoming Intel Knights Mill Phi, because in their approach, workloads that can benefit from the higher FLOPS enabled by FP16 will be getting them from the GPU or another accelerator.

Takeaway: While rival Intel is championing a big silicon approach for its x86 chips, IBM, along with CORAL partners Nvidia and Mellanox, believes the best way forward is to move work off the processor using accelerators and other intelligence offloading implementations.

“As we’re moving into the post-Moore’s law era, you can’t just turn the crank and make the general-purpose processor faster,” said Starke. “It’s our believe that you’re going to see more and more specialized silicon. That can be in the form of on-chip acceleration, but as you can see from our approach, we tend to believe it’s more flexible and deployable with off-chip acceleration. Obviously it requires extreme bandwidth, low-latency, and tight integration with your main processor complex, but that’s where we see the future of computing going and you see us putting very strong investments in these directions.”