Forget for a moment the prevailing high anxiety over Moore’s law’s fate. In the near-term – which could easily mean a decade – CMOS will remain the only viable, volume technology driving computing. Pursue alternatives? Of course, urged Josh Fryman, principal engineer and engineering manager, Intel. But more can and must be done to advance CMOS-based architecture and Intel, not surprisingly, has a few ideas.

Fryman was one of three speakers scanning the horizon at ISC2016’s Scaling Beyond the End of Moore’s Law session. It was fascinating conversation covering quantum computing, neuromorphic computing, and today’s workhorse, CMOS.

Damian Steiger, a researcher at the Platform for Advanced Scientific Computing and the Institute for Theoretical Physics of ETH Zurich, tackled quantum computing. Figuring out how to actually implement quantum computing and identifying killer quantum applications to attract needed funding formed much of his talk. He had three applications in mind although wasn’t especially optimistic we’ll see useful quantum computers anytime soon with the possible exception of government-funded efforts aimed at decrypting RSA.

Karheinz Meier from the Human Brain Project tackled neuromorphic computing. Here, the near-term future seems brighter. Meier expects the recent availability of three large-scale neuromorphic computing systems for application development to push progress more quickly. (See HPCwire article, Think Fast – Is Neuromorphic Computing Set to Leap Forward?)

It fell to Fryman, the opening speaker, to remind everyone that as promising as many new directional efforts look, it takes years to work out the bugs and turn a new technology into a large-scale manufacturing-friendly process. Interestingly, according to Fryman, advancing CMOS will mostly involve reviving old ideas that were problematic in the past but are unavoidable now. It will also require thinking far more holistically about how hardware and software play together.

“We need to find the Neo of the next generation [computational technology],” agreed Fryman, referring to the protagonist in the film, The Matrix, whose abilities jumped over those around him, “but once you find it, once you work out the techniques, you still have a long haul to make it something we could use, something viable for mass production.

“Until then what are we going to do? The short answer is CMOS is going to continue. It’s not because it is necessarily the best technology, it’s not because we particularly like it and adore it, it’s because we have no choice to keep everything moving forward.”

In setting the context for his talk, Fryman emphasized it’s important to remember that Moore’s law is a business statement not a technology law. That said, Moore’s law has become a surrogate for many things, including the pace of semiconductor technology advance. Its current “difficulties” (Dennard scaling, et al.) have, of course, been widely discussed with Intel holding strong against the growing opinion that Moore’s law’s days are numbered. (See HPCwire article, Moore’s Law – Not Dead – and Intel’s Use of HPC to Keep it Alive)

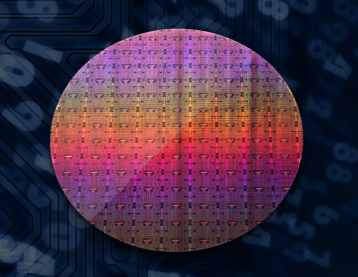

Fryman noted the classic recipe for engineers to achieve Moore’s law for transistors has been “to scale your dimensions, to scale your supply, and you’re done. You just keep turning the crank on this over and over. The running joke is years ago in the fab we used just a handful of elements in the periodic table. Today we use just about all of the elements except for a handful to get the same job done. [But at the end of the day] it’s still just a recipe.”

From an engineering perspective, what happens when the recipe fails? Fryman briefly reminded the audience that change is hardly new in electronics but that a few common underlying characteristics have been necessary for progress.

“If you look at the evolution of electronics, moving from mechanical to electromechanical, to vacuums tubes, to bipolar, to NMOS, to PMOS, and ultimately CMOS, and now you have this questions about what is coming. If you look at the trend line historically, each of the crossings is defined by having three basic components. You have to have gain; signal to noise control; and scalability, although scalability is really an overused term. What does it really mean? You’re talking about three dimensions: performance, energy, and pricing. These are the three fundamentals for something to actually be a viable technology and it needs to be ‘friendly to high volume manufacturing.’”

As there is no obvious technology to replace CMOS now, the focus must be on how to use what we know. This is doable, maintains Fryman, but will require rethinking existing approaches and in some instances re-learning old lessons. He said a trio of strategies will drive advances in underlying CMOS and compute architectures.

- Remove waste to reclaim efficiency. Die area, for example, has ballooned to accommodate accumulating features such as pipelines, onchip floating point, out-of-order execution, etc. In many cases performance, and in most cases power consumption, have suffered. Review of accumulated features with an eye towards simplification and elimination will play a role.

- Use known techniques. Over the years, lots of manufacturing and chip design approaches have been tried and tested and well characterized, including their drawbacks, “but people wanted to avoid them because they were considered hard at some level, too hard to program, to hard to use, too hard to design. But when you are running out of other knobs [to adjust] these are not as hard anymore.”

- Multidisciplinary solutions. Tackling physical manufacturing problems will only work so far; offloading or streamlining performance and tracking Moore’s law will require blended software, hardware, and manufacturing processes.

Far from pessimistic Fryman believes making further progress using these techniques is do-able, if challenging, and offered a few directional examples including one on handling resiliency at small feature size.

“Everybody is worried that once you get down to 7 nm you are going to have higher variability and failures and what am I going to do about it. There are two ways to look at it. There are reactive measures, so if something fails, an ECC failure, a soft upset, what am I going to do about it? I’ll have to react, I’ll have to kill, I’ll have to restart,” said Fryman.

“There’s also the proactive side which is I am going to plan ahead for this future and I am going to design my system in software and the hardware level to periodically check itself, to check if I am leading to a failure situation should I bring down my voltage, should I migrate work away from something.

“From a user experience. I have a classic software layer. I’ve got run time sitting on top of hardware, how does that interact with the entire stack. I’ve got user codes. I’ve got runtimes. I’ve got programming support tools. All these things need to be aware of the underlying assumptions in the system,” he said.

Power management is another area likely to involve tighter links between software and hardware. He cited work from a Polaris test chip in the 2006-2007 timeframe. “I can look at fine grained power management techniques. This is another known technique that’s way beyond clock handling. There are 21 dynamic sleeper readings in the actual tile, a whole bunch of tiles on the die, and you let the system turn the tiles on and off in the sleep state, which give a significant energy savings.”

Fryman again emphasized this is known technique but it’s hard do because it extends beyond hardware and has software implications: how do you structure your code, how do you know when you can take advantage of something like this, etc.

“We are going to have to start thinking outside the box and [in many instances] go back to existing techniques and say so, do we really need cache coherency across an entire machine. Maybe not. Do we really need cache coherency across 1000 cores on a die or 100 cores on a die, probably not. Are we willing to take the complexity from software for a simpler more efficient, more scalable hardware? Really what I am saying moving forward is we need to take your heads out of the sand, pardon the pun, and rethink what we have been doing,” he said.

Fryman says the industry is moving into another era that he calls “the disaggregation of the datacenter.” In a fully connected model, he said, there is “no system you can design that can get the bandwidth.” More and more compute will push out to the edges and “it will look different and this is where machine learning an other algorithms come in and neuromorphic might be a big deal. I see the industry not as stagnant but going through this shift to the edge, which is a very different design point than the classic PC or tablet.”

The Intel engineer was careful not to reveal too much, “Eventually turning the knob on transistors, as we have been doing, will not work. When that is is highly debatable, which is why I chuckle. I’m not supposed to talk about post 7 nm but I can simply say it’s actively being looked into.”