While commercial application isn’t imminent researchers have successfully scaled storage down to the classical limit of a single atom according to work reported in Nature last week. An international team of researchers, using a scanning tunneling microscope (STM) at the IBM Almaden Researcher Center, were able write and read bits using single holmium (Ho) atoms.

‘The single-atom bit represents the ultimate limit of the classical approach to high-density magnetic storage media. So far, the smallest individually addressable bistable magnetic bits have consisted of 3–12 atoms. Long magnetic relaxation times have been demonstrated for single lanthanide atoms in molecular magnets for lanthanides diluted in bulk crystals, and recently for ensembles of holmium (Ho) atoms supported on magnesium oxide (MgO). These experiments suggest a path towards data storage at the atomic limit,” write authors of the Nature Letter, “Reading and writing single-atom magnets.”

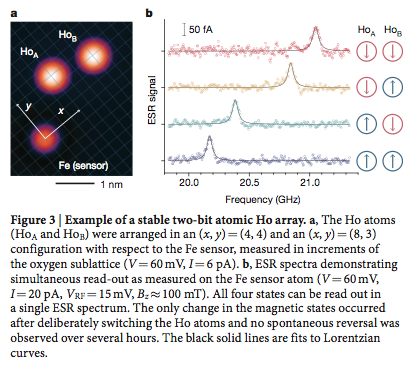

Many theoretical and practical issues remain. For instance, no one is quite sure of the mechanism by which Ho atoms retain their “relaxation” period. Nevertheless, the researchers, led by Andreas Heinrich, director of the Center for Quantum Nanoscience in the Institute of Basic Science, South Korea, were able to construct a two-bit atomic Ho array (figure below) as a proof of concept.

In describing the work for Nature in its News & Views section, Robert Sessoli of the University of Florence (which is unaffiliated with the work) called it an unambiguous demonstration that writes/reads at the single atom scale are possible.

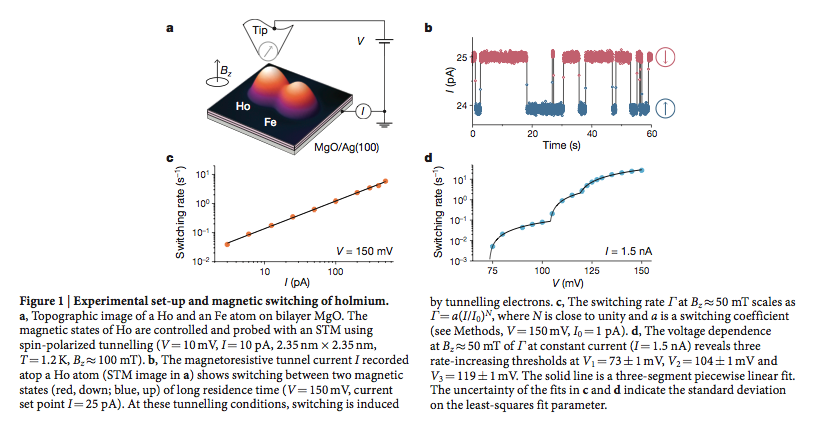

The authors write, “Here we address the magnetic bistability of individual Ho atoms on MgO, which we switch using current pulses and detect through the tunnel magnetoresistance using a spin-polarized scanning tunnelling microscope (STM). We unambiguously prove the magnetic origin of the switching in the tunnelling resistance using STM-enabled single-atom electron spin resonance (ESR) on an adjacent iron (Fe) sensor atom. Additionally, we determine by this method the out- of-plane component of the Ho magnetic moment, and use the long lifetime to store two bits of information in an array of two Ho atoms whose magnetic state can be read locally by magnetoresistance, and remotely by means of ESR on a nearby sensor atom.” (See figure of experimental set-up below.)

In summing up his view of the research, Sessoli wrote: “Although (Fabiano) Natterer and colleagues’ work is still far from having real-world applications, their advancement of scanning probe microscopy techniques has shown that the storage and retrieval of magnetic information in a single atom is feasible. Several issues need to be resolved. In terms of reading and writing data, the techniques involved are not the most user-friendly or affordable. Even if other sensing methods are developed, the peculiar magnetic properties of Ho atoms exploited by the authors can be realized only in extreme conditions, such as in an ultrahigh vacuum.”

Link to Nature Letter: http://www.nature.com/nature/journal/v543/n7644/full/nature21371.html

Link to Nature News & Views: http://www.nature.com/nature/journal/v543/n7644/full/543189a.html

Authors: Fabian D. Natterer1,2, Kai Yang1,3, William Paul1, Philip Willke1,4, Taeyoung Choi1, Thomas Greber1,5, Andreas J. Heinrich6,7 & ChristopherP.Lutz1

1, IBM Almaden Research Center, San Jose, California 95120, USA; 2, Institute of Physics, École Polytechnique Fédérale de Lausanne, CH-1015 Lausanne, Switzerland; 3, School of Physical Sciences and Key Laboratory of Vacuum Physics, University of Chinese Academy of Sciences, Beijing 100049, China; 4, IV. Physical Institute, University of Göttingen, Friedrich-Hund-Platz 1, D-37077 Göttingen, Germany; 5, Physik-Institut, Universität Zürich, Winterthurerstrasse 190, CH-8057 Zürich, Switzerland; 6, Institute of Basic Science, Center for Quantum Nanoscience, Seoul, South Korea; 7, Physics Department, Ewha Womans University, Seoul, South Korea.