Spintronics has for some time been a promising research area in efforts to develop alternative computing systems. Among its many prospects are smaller ‘transistor’ size, higher speeds, lower power consumption, and innovative architecture. This week a group of researchers led by Joseph Friedman of the University of Texas, Dallas, report in Nature Communications development of an all-carbon spintronic system in which spintronic switches function as gates.

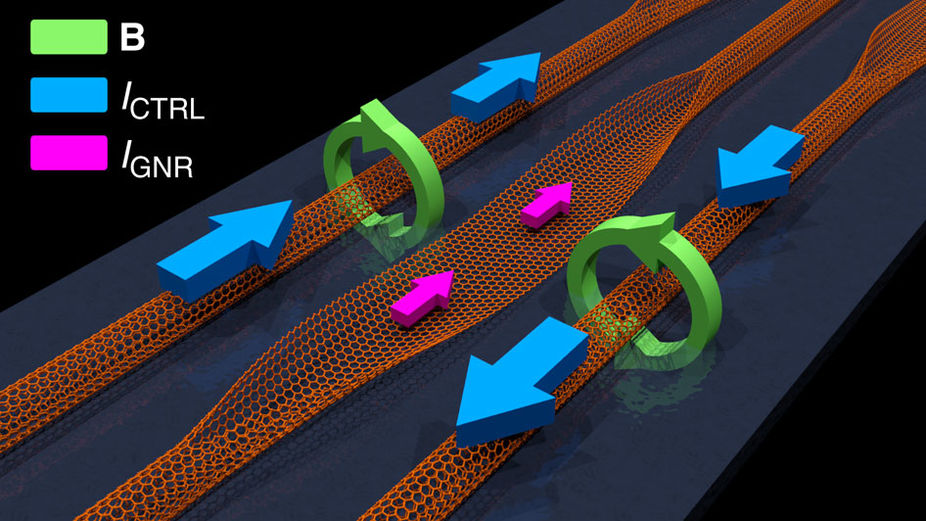

“The all-carbon spintronic switch functions as a logic gate that relies on the magnetic field generated when an electric current moves through a wire. In addition, the UTD researchers say a magnetic field near a graphene nanoribbon affects the current flowing through the ribbon. Transistors cannot exploit this phenomenon in silicon-based computers, but in the new spintronic circuit design, electrons moving through carbon nanotubes (CNT) create a magnetic field that impacts the flow of current in a nearby graphene nanoribbon (GNR), providing cascaded logic gates that are not physically connected,” notes ACM TechNews in a description of the work.

Since communication between each of the graphene nanoribbons takes place via an electromagnetic wave, the researchers predict communication will be much faster, with the potential for terahertz clock speeds. At least that’s the hope. The new work is significant on several fronts, not least for providing a design that can be tested.

Friedman and his collaborators write in their Nature article (Cascaded spintronic logic with low-dimensional carbon), “Though a complete all-carbon spin logic system is several years away from realization, currently available technology permits experimental proof of the concept as shown [here]. By exploiting the exotic behavior of GNRs and CNTs, all-carbon spin logic enables a spintronic paradigm for the next generation of high-performance computing.”

“The concept brings together an assortment of existing nanoscale technologies and combines them in a new way,” says Friedman in an account of the work on the UT Dallas website (Engineer Unveils New Spin on Future of Transistors with Novel Design).

As shown below (taken from the paper), the active switching element is a zigzag GNR field-effect transistor with a constant gate voltage and two CNT control wires. The gate voltage is held constant, and the GNR conductivity is therefore modulated solely by the magnetic fields generated by the CNTs. “These magnetic fields can flip the orientation of the strong on-site magnetization at the GNR edges, which display local antiferromagnetic (AFM) ordering due to Hubbard interactions,” according to the paper.

“Remarkable breakthroughs have established the functionality of graphene and carbon nanotube transistors as replacements to silicon in conventional computing structures, and numerous spintronic logic gates have been presented. However, an efficient cascaded logic structure that exploits electron spin has not yet been demonstrated. In this work, we introduce and analyse a cascaded spintronic computing system composed solely of low-dimensional carbon materials,” write the researchers.

“We propose a spintronic switch based on the recent discovery of negative magnetoresistance in graphene nanoribbons, and demonstrate its feasibility through tight-binding calculations of the band structure. Covalently connected carbon nanotubes create magnetic fields through graphene nanoribbons, cascading logic gates through incoherent spintronic switching. The exceptional material properties of carbon materials permit Terahertz operation and two orders of magnitude decrease in power-delay product compared to cutting-edge microprocessors. We hope to inspire the fabrication of these cascaded logic circuits to stimulate a transformative generation of energy-efficient computing.”

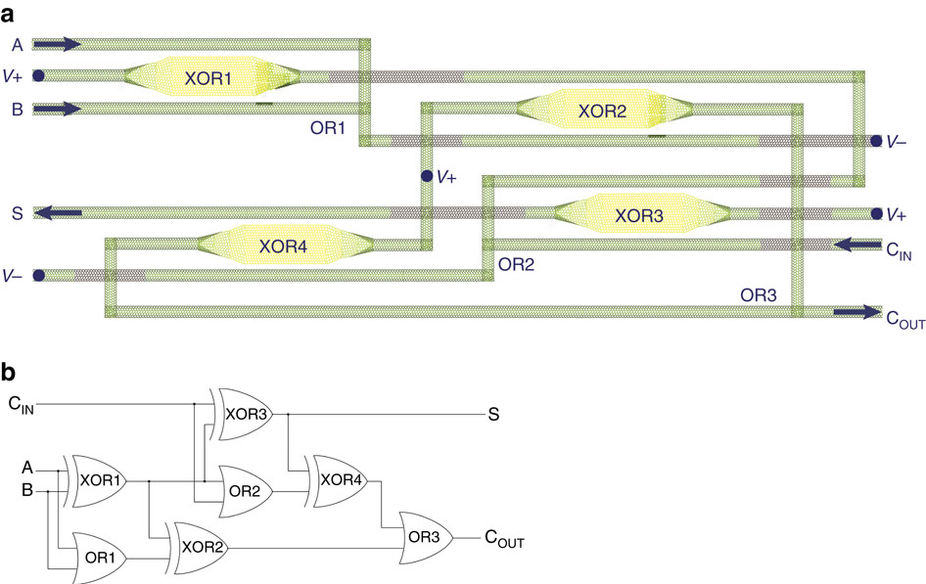

Shown here is a conceptual spintronic-based 1-bit adder circuit.

“This was a great interdisciplinary collaborative team effort,” Friedman said, “combining my circuit proposal with physics analysis by Jean-Pierre Leburton and Anuj Girdhar at the University of Illinois at Urbana-Champaign; technology guidance from Ryan Gelfand at the University of Central Florida; and systems insight from Alan Sahakian, Allen Taflove, Bruce Wessels, Hooman Mohseni and Gokhan Memik at Northwestern.”

Link to Nature Communications article: https://www.nature.com/articles/ncomms15635

Link to UTD article: http://www.utdallas.edu/news/2017/6/5-32589_Engineer-Unveils-New-Spin-on-Future-of-Transistors_story-wide.html?WT.mc_id=NewsHomePageCenterColumn

Images: Nature