Standards group JEDEC announced the publication of the DDR5 SDRAM spec, the next-generation standard for random access memory (RAM). Compared to DDR4, the DDR5 spec delivers twice the performance and improved power efficiency, addressing ever-growing demand from datacenter and cloud environments, as well as artificial intelligence and HPC applications.

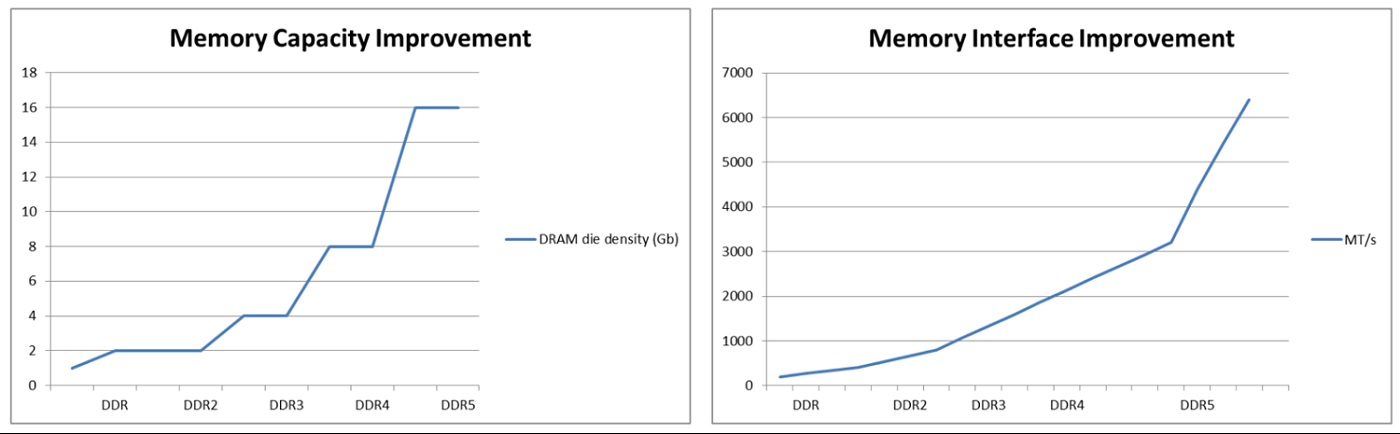

Providing up to 6.4 Gbps, DDR5 doubles the bandwidth of its predecessor, DDR4, which tops out at 3.2 Gpbs. At launch, DDR5 modules will reach 4.8 Gbps, providing a 50 percent improvement versus the previous generation. Density goes up four-fold with maximum density increasing from 16 Gigabits per die to 64 Gigabits per die in the new spec. JEDEC representatives indicated there will be both 8 Gigabit and 16 Gigabit DDR5 products at launch.

DDR5 boosts signaling rates to 6,400 MT/s, but Desi Rhoden, chairman, JEDEC JC-42 memory committee, and executive vice president of Montage Technology, says there are discussions about going beyond that. “I think you can expect that you might see something above that as well — and much improved channel utilization,” he said in a press briefing held earlier this week.

A new feature, Decision Feedback Equalization, was added to improve IO speed scalability. “It enables us to build really high frequency interfaces,” said Rhoden. “We didn’t need this before because we were at performances that did not demand it, but now we have to use equalization to get to the high speed IO. And this is the first time we’ve ever had it in the DRAM itself. We’ve had it in support logic before but the first time in the DRAM itself.”

A fine grain refresh feature, all bank refresh, improves 16 Gigabit device latency. Same bank refresh offers the ability to refresh in one part of the die while other parts are in use, providing higher utilization.

Additional features/specs include:

• On-die ECC and other scaling features enable manufacturing on advanced process nodes.

• Improved power efficiency enabled by Vdd going from 1.2V to 1.1V as compared to DDR4.

• Use of the MIPI Alliance I3C Basic specification for system management bus.

• At the module level, voltage regulator on DIMM design enables pay as you go scalability, better voltage tolerance for improved DRAM yields and the potential to further reduce power consumption.

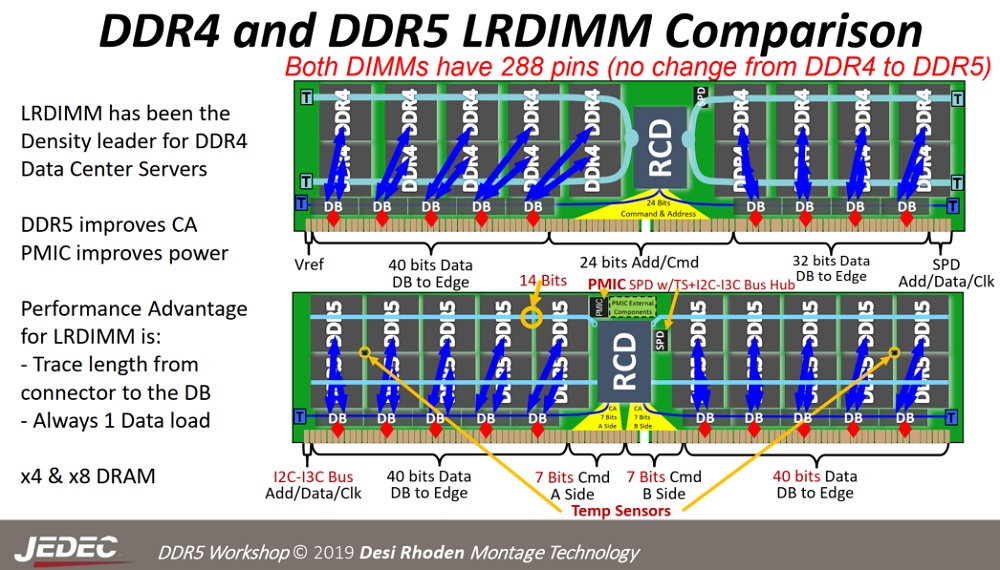

• The DIMM has two 40-bit (32 data bits plus eight ECC bits) independent sub-channels on the same module for efficiency and improved reliability.

The DDR5 spec also increases stacking capability, doubling the height from the previous generation. “The DDR4 spec defines up to an 8-high stack, and for most of the industry the maximum stack height was 4-high. For DDR5, we have defined up to a 16-high stack, and expect up to 8-high stack products,” said Johnny Kim, chairman, JEDEC JC-42.3C subcommittee and staff engineer, memory product planning and enabling at Samsung.

With a DDR5 DIMM supporting 40 placements of DRAM, an 8-high stack at 64 gigabits per die brings the upper capacity to 2 terabytes.

Devices are sampling now and CPUs are available to work with them, JEDEC said. Historically, it’s taken about 18 months to transition from one generation to the next and the JEDEC representatives expect that trend to hold with the server market leading. “The server datacenter market led for the transition to DDR4 back in 2014, and the datacenter market has grown substantially since that time. So we think that that’ll [even more so] be the snowplow for DDR5 adoption,” said Paul Fahey, JEDEC board of directors and vice president DRAM technology at SK hynix.

The previous two DDR generations have come at about a seven-year cadence, and this longevity, along with the demands of the data age, set a high bar for the DDR5 spec and roadmap. “These generations always live longer than initially anticipate them to live,” said Rhoden. “DDR5, because it does have so much capability built into it, has the potential to live quite a long life.”

“We added a lot into the spec to give it that longevity,” noted Frank Ross, JEDEC board of directors and senior member of technical staff, lead architect, Micron. “Whether we use all of those features and all of the capacities and so forth is yet to be seen. But we’ve seen each subsequent DRAM generation last longer than previous one as new applications come around. We’ve improved DRAM reliability quite a bit over the years. You have applications that will continue to use DDR3 and DDR4 for a long time, and I imagine DDR5 will be the same.”

Going forward though, the expectation is that all new designs will be focused on the newest standard. “To take advantage of the kinds of things that DDR5 offers, I think people will be wanting to design in it and as quickly as possible,” said Ross.

“We’ve got probably the best standard we’ve ever produced,” Ross added. “I think the industry is going to be very impressed. And everyone has to remember, DDR5 is a system level solution. So we’re producing a component spec at the same time we’re producing a module spec, as well as support components. So there’s just a tremendous amount of work that goes into the spec and in the end, we have an extremely high quality document.”

Over 150 companies were involved in the creation of this spec. Micron, Samsung, SK hynix, Synopsys, Intel and AMD are among the companies expressing their support and engagement.

Micron Technology, which announced DDR5 RDIMM samples in January (2020), is now launching an enablement program to provide early access to technical resources, products and ecosystem partners. The program will aid in the design, development and qualification of next-generation computing platforms that use DDR5, said Mircon.

SK Hynix has been working on DDR5 samples since 2018, and expects to start mass manufacturing by the end of this year.

Synopsys introduced the industry’s first JEDEC DDR5 compliant Verification IP (VIP) for DDR5 DRAM/DIMM to enable the design and verification of next-generation memory devices.

The DDR5 SDRAM (JESD79-5) spec document is available for download from the JEDEC website.