FPGA vendor Xilinx has debuted its latest SmartNIC model, the Alveo SN1000, with integrated “composability” features that allow enterprise users to add their own custom networking functions to supplement its built-in networking.

By providing deep flexibility and customization, the Alveo SN1000 gives customers, including hyperscalers, cloud users and a wide range of enterprise users, tools that will give them the ability to create the custom network capabilities needed by their organizations, according to Xilinx.

The new SN1000 SmartNIC was unveiled by the company on Feb. 23 (Tuesday), along with a new accelerated algorithmic trading platform and a new Xilinx FPGA app store where customers can find FPGA applications they need in one place.

Inside the Alveo SN1000 SmartNICs

Built into the latest SN1000 SmartNICs are the adaptability of Xilinx Field Programmable Gate Arrays (FPGAs), isolated control and data planes and the company’s Vitis Networking, which allows P4, C and C++ programming by developers. The SN1000s offer software-defined hardware acceleration for all function offloads, which when combined with its other features allows customers to designate workloads to components as needed for peak situational performance.

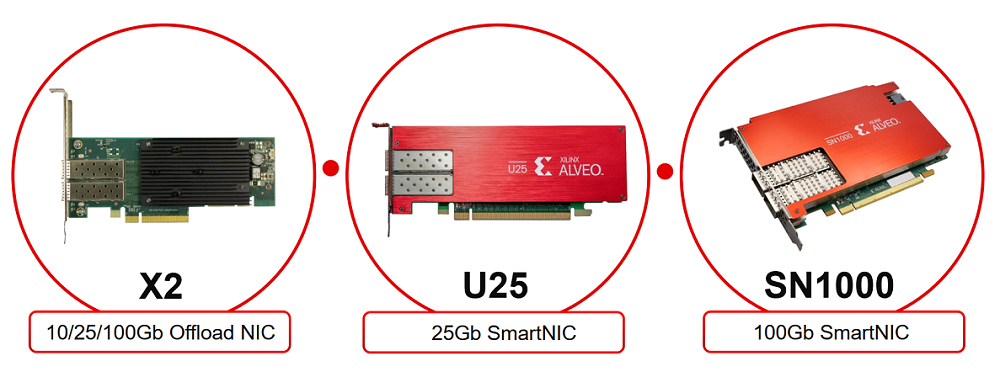

Using an open architecture, the new 100Gb/s SmartNICs directly offload CPU-intensive tasks to optimize networking performance for users, according to Xilinx. With the new SmartNICs, the company hopes to make it easier for software developers to create and deploy software-defined, hardware-accelerated applications on Alveo accelerator cards.

For customers, these features mean they can get off-the-shelf network functions from Xilinx while also being able to add their own needed functions and services and chain them together seamlessly, Pejman Roshan, the vice president of marketing in the company’s datacenter group, said in an interview.

“That service chaining isn’t a new concept, but the fact that it’s plumbed into the hardware pipeline in the manner which [a customer] decides what works best for [them and their organization] …that’s what’s innovative here. This is the first [to do that].”

Traditional standard NICs used to be the preferred choice for datacenter deployments in the past, Kartik Srinivasan, director of marketing for the SmartNIC team at Xilinx, explained. “They were responsible for packet traffic coming in and out of the server, in and out of the storage from the network. But they started putting a burden on the CPU when you started approaching the 25Gb speeds and higher. That’s when the offload mix came into existence and provided some relief.”

In earlier SmartNIC designs “the CPU took away a lot of the packet processing from the host into the standard NIC and by itself, most of them were ASIC-based (Application-Specific Integrated Circuit) implementations.” Those designs provided limited offloads depending on the capabilities of each device, said Srinivasan.

Based on the company’s 16nm UltraScale+ architecture, the SN1000 SmartNICs are powered by the low-latency Xilinx XCU26 FPGA and a 16-core Arm processor. SN1000 SmartNICs deliver dual-QSFP ports for 10/25/100Gb/s connectivity with leading small packet performance and a PCIe Gen 4 interconnect. The cards are available in a full height, half length (FHHL) form factor in a 75-watt power envelope.

The SN1000 SmartNICs can be used for a wide range of networking, security, and storage offloads, such as Open vSwitch and virtualization acceleration, according to Xilinx. The Alveo SN1000 SmartNICs are expected to be generally available in March 2021.

The SmartNIC marketplace has been accelerating in recent years as customer demand has risen in reaction to new designs that provide greater performance and improved expandability.

The big chip companies have been noticing trends like these, with AMD revealing its $35 billion acquisition of Xilinx in October 2020, helping AMD to keep pace during a time of consolidation in the semiconductor industry. GPU rival and market leader Nvidia made two big moves of its own in the last 23 months–announcing its intentions in September 2020 to acquire chip IP vendor Arm for $40 billion, and the completion of its $6.9 billion acquisition of interconnect vendor Mellanox. The Mellanox deal quickly got Nvidia firmly entrenched in DPUs of its own, as well as in networking innovations that are now being woven into its core markets.

A Unique SmartNIC Advancement: Analyst

Baron Fung, a server and server connectivity analyst with Dell’Oro Group, said he sees the heterogeneous architecture of the SN100—using both an Arm processor and an FPFGA—as “unique” in the marketplace. “This design allows end users the flexibility to customize the FPGA for a wide range of offload applications without compromising control plane functionality and reducing latency,” said Fung.

“Generally, one of the big hurdles in SmartNIC deployments is that the software development is lengthy and resource intensive, requiring teams of engineers that are versed in VHDL (VHSIC Hardware Description Language),” said Fung. “However, the SN1000 is compatible with programming such as P4, C and C++ that are commonly used by a wide range of data center networking equipment. In addition, the SN1000’s composable design enables end-users to insert and rearrange accelerator modules within the data path to shorten software development lead-time.”

While SmartNICs are generally used primarily in the hyperscale cloud market, the SN1000 should also appeal to a wide range of segments, from hyperscale cloud users to enterprise companies, said Fung. “More sophisticated hyperscale companies can customize the SN1000 starting from a clean slate, or enterprise customers can use accelerator modules that have been pre-programmed by Xilinx.”

In a recently published five-year forecast for the SmartNIC market, the Dell’Oro Group sees the segment growing from $245 million in 2020 to more than $1 billion by 2025, for a 33 percent compound annual growth rate (CAGR), said Fung.

Easing Algorithmic Trading

Xilinx also debuted an accelerated algorithmic trading (AAT) reference design for l0w-latency trading that addresses one of the main barriers to entry for high-frequency trading.

“Achieving sub-microsecond latency in algorithmic trading has traditionally required costly and time-consuming hardware development,” the company said in a press release. “The Vitis development platform now includes an accelerated algorithmic trading reference design which gives software developers the ability to quickly and cost-effectively deliver sub-microsecond trading performance without the need for custom hardware development.”

Xilinx says it has created a modular design that includes all the components for an end-to-end, low-latency trading solution that customers can further customize using C and C++ in the Vitis platform. The AAT reference design is available to Alveo customers at no cost.

Xilinx’s New FPGA App Store

Also announced by Xilinx is its new FPGA app store, which is built to include ready-to-deploy accelerated applications spanning Smart World AI video analytics to anti-money laundering and live video transcoding. Developed by Xilinx ecosystem partners, the containerized pre-built applications provide an easy way for customers to quickly find, evaluate, purchase and deploy accelerated applications to meet their requirements.

A version of this article first appeared on HPCwire sister site EnterpriseAI.