Following their debut launch in November, AMD Epyc processors with 3D V-Cache technology, codenamed Milan-X, are now generally available from major system-makers as well as from cloud provider Microsoft Azure. Available in four SKUs and ranging from 16- to 64-cores, the new processors feature 768 megabytes of L3 cache and are compatible with existing platforms after a BIOS upgrade.

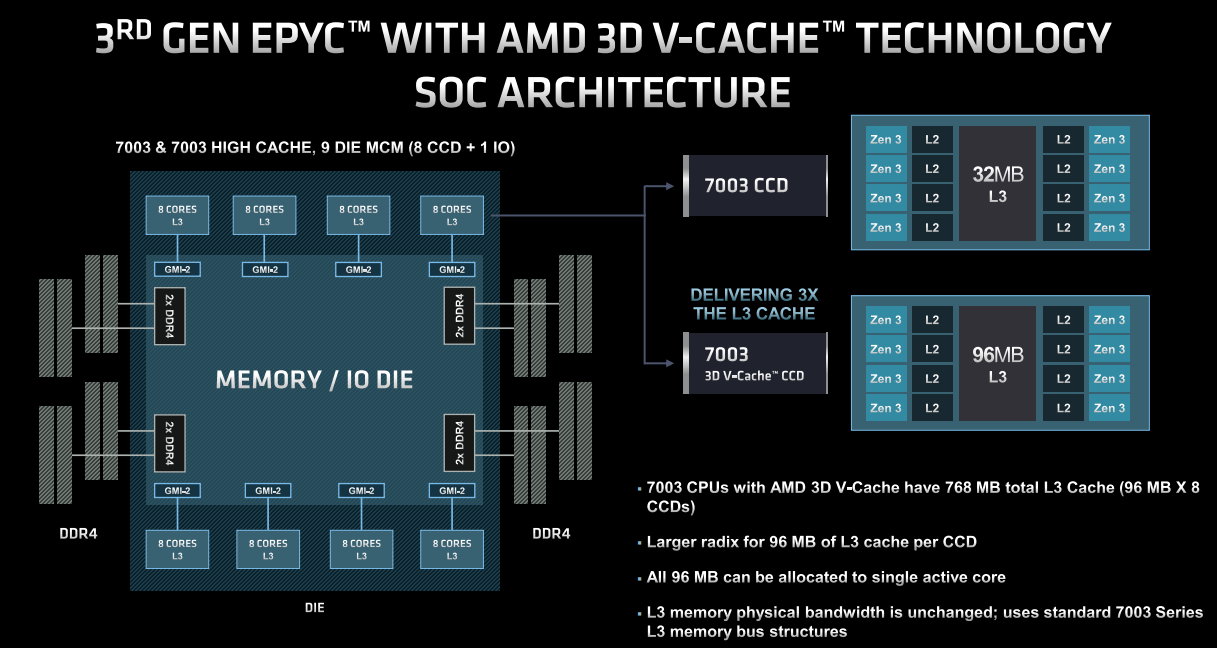

The new Milan-X processors are AMD’s first server CPUs with 3D chiplet technology, implementing what AMD says is “true 3D die stacking.” Built on the same TSMC 7nm Zen 3 cores as Milan, the Milan-X processors have three times the L3 cache compared to standard Milan parts. In Milan, each complex core die (CCD) had 32 megabytes of cache; Milan-X adds 64 megabytes of 3D stacked cache on top for a total of 96 megabytes per CCD. With eight CCDs, that adds up to 768 megabytes of L3 cache. Adding in L2 and L1 cache, there is a total of 804 megabytes of cache per socket.

Milan-X with 3D V-Cache employs a hybrid bond plus through silicon vias to overcome the physical limitations of 2D chip designs. The die-to-die interface uses a direct copper-copper bond with no solder bumps to connect the Zen 3 core to the cache module, improving thermals, transistor density and interconnect pitch.

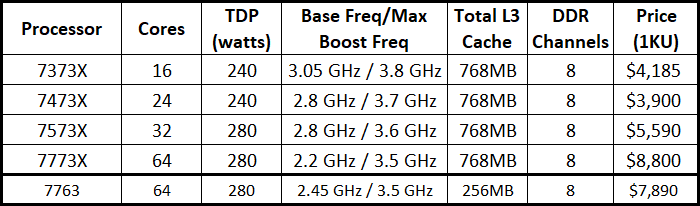

The Epyc 7003X-series family is available in four standard SKUs: the 16-core, 240-watt 7373X listing for $4,185; the 24-core, 240-watt 7473X for $3,900; the 7573X, 280-watt, for $5,590; and the top-bin 64-core, 280-watt 7773X for $8,800 (priced based on 1,000 units). With nearly equivalent frequencies and TDPs, the 64-core Milan-X has a similar profile to the standard 64-core Milan 7763 — however, the 3D V-Cache technology provides three times more cache for the new CPU.

AMD indicated that the Milan-X processors were engineered to fit within the power and thermal frameworks of the existing Milan high-frequency parts to provide customers choice within the same server platform. Prices for Milan-X products represent about a 20 percent increase over their equivalent Milan high-frequency parts, according to AMD.

In pre-briefing materials provided to HPCwire, AMD clarified that not all workloads would benefit from the V-Cache technology, but provided examples (with representative benchmarks) of where it would make the most sense.

“Workloads that may be a fit for Milan-X [are] sensitive to L3 cache size, have high L3 cache capacity misses – i.e., the data set is often too large for L3 cache – or have high L3 cache conflict misses – i.e., the data pulled into cache has low associativity,” the company stated.

“Workloads that likely won’t benefit from Milan-X already have L3 cache miss rates near zero, have high L3 cache coherency misses – i.e., data is highly shared between cores – and may be CPU-intensive, but only ‘stream’ data or use it once rather than operating on it iteratively,” AMD also said.

AMD reports performance improvements for Milan-X across targeted technical computing workloads, spanning computational fluid dynamics (CFD), finite element analysis (FEA), electronic design automation (EDA), weather forecasting and other domains.

In internal testing conducted by AMD, the 16-core Milan-X CPU delivered 66 percent faster simulations on Synopsys VCS when compared to the standard 16-core Milan CPU. This worked out to an average of 24.4 jobs per hour without 3D V-Cache, and 40.6 jobs per hour with 3D V-Cache. An EDA workload, VCS is used by many of the world’s top semiconductor companies to catch defects early in the development process before a chip is committed to silicon.

“The volume of cores that Synopsys VCS runs on in the latest 3rd gen AMD Epyc processors is massive,” said Sandeep Mehrotra, vice president of engineering, Synopsys, in a statement. “With the significant memory and cache required by today’s compute-intensive EDA workloads, the memory efficiency at runtime with VCS is exceptional and gives us a big competitive edge. Our close collaboration with AMD continues to accelerate technology advances for our customers by empowering them to tackle verification challenges and complexity of tomorrow’s SoCs.”

Putting a top-of-stack 64-core Milan-X (7773X) processor against an Intel 40-core Platinum 8380 processor, AMD showed workload speedups of up to 44 percent (Altair Radioss), up to 47 percent (Ansys Fluent), up to 69 percent (Ansys LS-Dyna) and up to 96 percent (Ansys CFX).

On the same application set, average core-to-core comparisons between the 32-core Milan-X (7573X) and the 32-core Xeon Platinum 8362 processor demonstrated performance uplifts for Milan-X of up to 37 percent (Altair Radioss), up to 23 percent (Ansys Fluent), up to 47 percent (Ansys LS-Dyna), and up to 88 percent (Ansys CFX).

AMD’s competitive comparisons were made against Intel’s Ice Lake platform, while Intel’s coming-gen Sapphire Rapids platforms are, according to Intel, gearing up to ship to select customers this quarter. It’s reasonable to expect counter benchmarking comparisons will be forthcoming.

Being able to run more workloads with less hardware ideally translates to reduced power consumption in the datacenter. Using the same competitive test scenario as above – the 32-core Epyc 7573X versus the 32-core Xeon 8362 – AMD said it was able to cut the number of servers used to run 4,600 Ansys cfx-50 jobs from 20 to 10, resulting in a power savings of 49 percent and a projected TCO savings of 51 percent over three years.

Launch Partners

Cloud provider Microsoft Azure, which in November announced its intention to switch all of its HBv3 instances over to Milan-X, states that upgrade has been completed.

“Azure HBv3 Virtual Machines, now fully upgraded to 3rd Gen AMD Epyc processors with AMD 3D V-Cache technology, … are the fastest adopted addition to the Azure HPC platform ever with performance gains of up to 80 percent on key HPC workloads,” said Nidhi Chappell, general manager, Azure HPC, AI, SAP and Confidential Computing, in a statement.

Memory company Micron is another launch partner and an early adopter.

“Micron and AMD share a vision of delivering full capability of leading DDR5 memory to high-performance datacenter platforms,” said Raj Hazra, senior vice president and general manager of the compute and networking business unit at Micron, in a statement. “Our deep collaboration with AMD includes readying AMD platforms for Micron’s latest DDR5 solutions as well as bringing 3rd Gen AMD Epyc processors with AMD 3D V-Cache technology into our own datacenters.”

For select EDA workloads, Hazra reported that Micron is seeing a 40 percent performance improvement by employing AMD Eypc processors with 3D V-Cache technology compared to the equivalent Epyc processors without the 3D V-Cache.

Other companies that have announced their support include system builders Atos, Cisco, Dell Technologies, Gigabyte, HPE, Lenovo, QCT and Supermicro – many of which have Milan-X platforms available today. ISV partners include Altair, Ansys, Cadence, Dassault Systèmes, Siemens and Synopsys.