The first numbers of the available bandwidth between chiplets are out – UCIe is estimating that chiplet packages could squeeze out communication speeds of 630 GB/s, or 0.63 TB/s, in a very tight area.

That number was shared by the Universal Chiplet Interconnect Express consortium last month during a presentation at ISC 2023. The consortium is developing UCIe, which is emerging as a universal interconnect to connect different silicon modules on a chiplet package.

Chip designers and manufacturers are breaking up big chip design into small pieces via chiplets, which are silicon modules that are assembled in one package. The chiplet approach can combine a wide range of accelerators and technologies in a single package. The current approach of throwing everything in one integrated chip is becoming cost prohibitive.

Chiplets are also beneficial by enabling silicon made on different nodes to be packaged together. For example, mixed signal chiplets made on older nodes could be combined with dense subsystems made on newer process nodes.

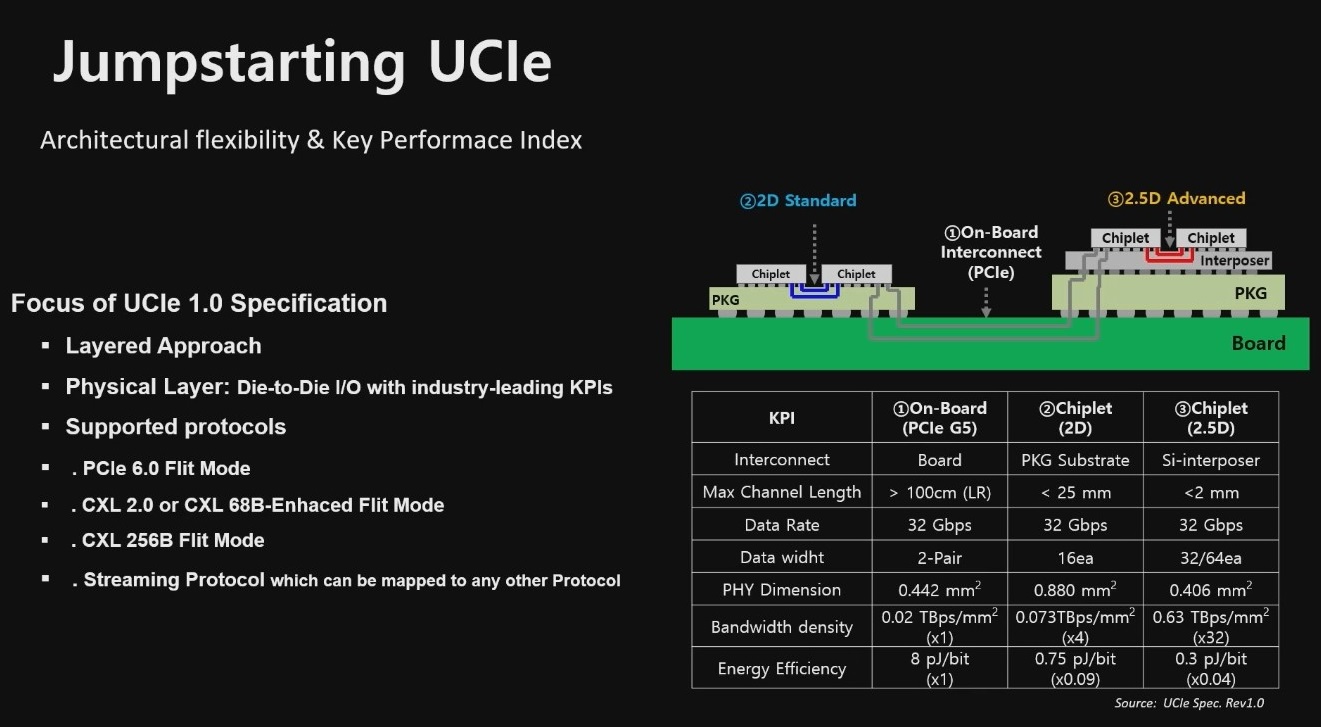

The UCIe interconnect will come in two versions – one is a standard version for 2D packaging, which will top out at 73 GB/s (or 0.073 TB/s) in four channels, which is fewer pipes than a standard PCIe Gen5 connection. The other is an UCIe advanced version for 2.5D packaging, which will have a bandwidth of 630 GB/s in 32 channels.

“As you move on-board to the package and from package to UCIe, the performance of the connectivity is improving by orders of magnitude and the efficiency you gain is getting even better,” said Cheolmin Park, vice president at Samsung Electronics, during the presentation.

The UCIe interconnect will be much denser than standard PCIe on-board connections, with bandwidth measurements done per millimeter-square. The UCIe-Standard interconnect will be 10 times more energy efficient than PCI Gen5. UCIe-Advanced will be four times more energy efficient than UCIe-Standard.

UCIe-Advanced will provide “the most advanced efficiency with highest bandwidth,” Park said.

UCIe is based on PCIe Gen5 electricals, and supports CXL 2.0. UCIe does not cover 3D packaging, and is a work in progress, Park said.

“We have a roadmap, and we are going to try and address it. The question is when the industry wants to see us doing it,” Park said.

He later added “we have a roadmap of providing the technology for optical solutions as well,” indicating a standard for optical interconnects in chiplets.

There are many ongoing efforts underway, including bringing memory into chiplet packages. That is especially important as memory bandwidth is a major bottleneck in computing subsystems today, Park said.

Bringing memory into the chiplet packaging is a natural progression of chip development. Currently memory communicates with logic through on-board connections, which will move into 3D chip packages.

UCIe is very seriously also considering supporting the automotive industry. Autonomous cars are getting a centralized computing subsystem by packaging multiple silicon modules into one cohesive package.