On May 17, 2017, a ceremony was held during the PRACEdays 2017 conference in Barcelona to announce the memorandum of understanding (MOU) between PRACE in Europe, RIST in Japan, and XSEDE in the United States. The MOU allows for the promotion and sharing of resources between the organizations, including PRACE’s federated resources in Europe, the K computer and other systems in Japan, and XSEDE’s network of HPC systems and advanced digital services in the US.

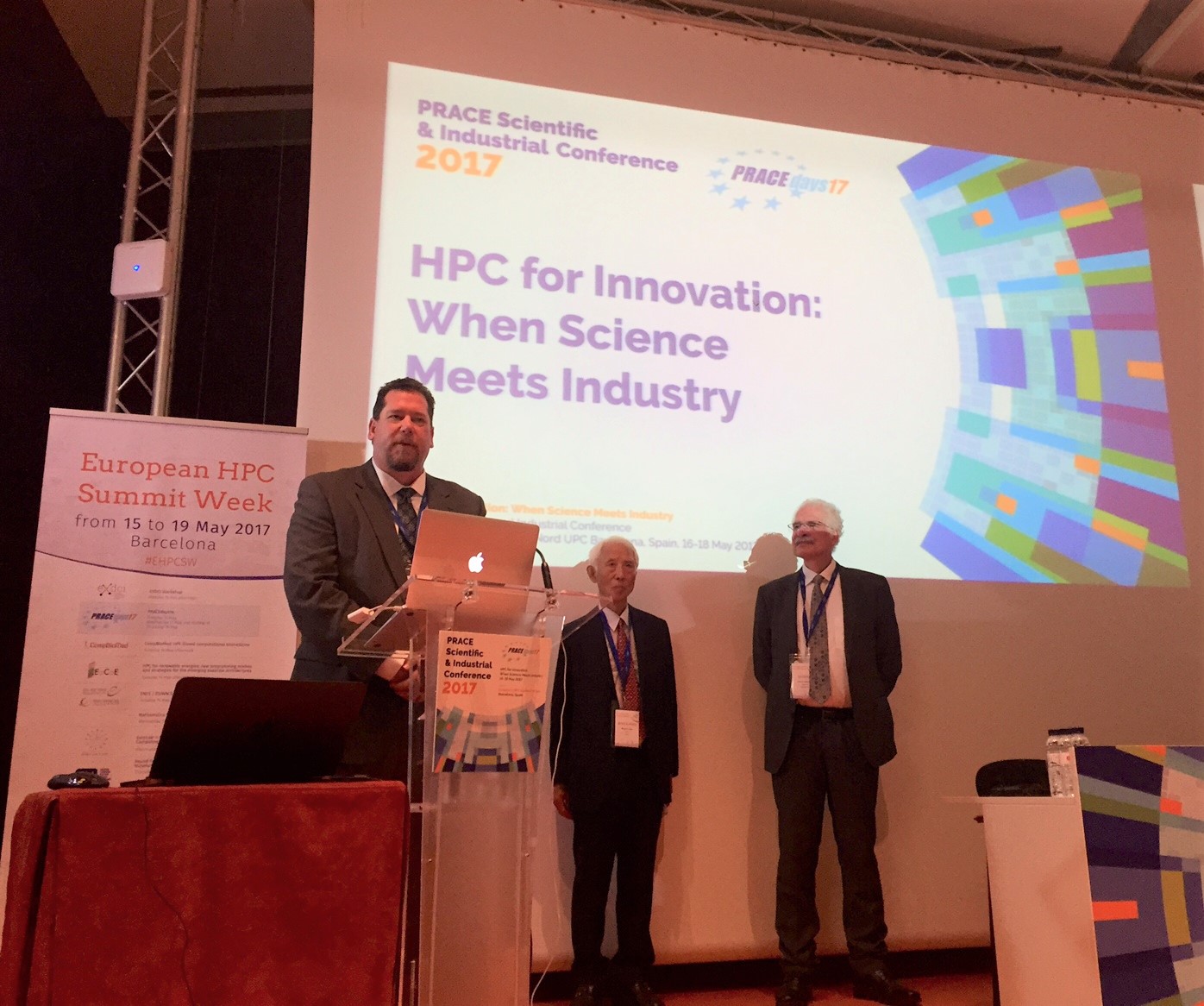

Discussing details of the enhanced partnership were Dr. Anwar Osseyran, council chair of the Partnership for Advanced Computing in Europe (PRACE); John Towns, principal investigator and project director for the Extreme Science and Engineering Discovery Environment (XSEDE); and Masahiro Seki, president of the Research Organization for Information Science and Technology (RIST).

“The aim is to stimulate collaboration in the area of research and computational science by sharing information on the usage of supercomputers,” said Dr. Osseyran. “The collaboration will be of mutual benefit, reciprocity and equality and we will identify the capabilities of cooperation in the areas of science, technology and industry. [Further, the MOU] will reinforce the HPC ecosystems for all of us.”

The agreement builds on the partners’ work with the International HPC Summer School. (The eighth such event will take place June 25 to June 30, 2017, in Boulder, Colorado, United States. Compute Canada is also a partner.)

“As research becomes much more an international endeavor, the need for infrastructure to collaborate closely and support those research endeavors becomes even more important,” said John Towns. “Having the agreement such as the one we have signed now facilitates the collaboration of the infrastructures and allows us to promote science and engineering and industry work and the use of HPC resources and very importantly the associated services and support staff that surround them. Being able to effectively use these resources is quite important and often they are very difficult as the technology moves very rapidly, so having access to the expertise is also critical. I’m very happy to be a part of this and I look forward to our work [together].”

“The three parties — PRACE, XSEDE and RIST — have recognized the importance of trilateral collaboration,” said Masahiro Seki. “Finalizing the MOU today makes me happier than anything else. In the new MOU, we will continuously implement exchange of information in the area of promotional shared use of supercomputers; at the same time our collaboration will be accelerated through the users of all the members of the partnering organizations, and especially the trilateral union will be of great help to promote advanced supercomputing in the field of science and technology and in industry.”

The ceremony commemorates the official signing which took place on April 4, 2017. The agreement contains the following elements:

(1) Exchange of information: Mutual exchange of experiences and knowledge in user selection and user support etc. is helpful for the three parties in order to execute their projects more effectively and efficiently.

(2) Interaction amongst the staff of the parties in pursuing any identified collaboration opportunities: Due to the complex and international nature of science, engineering and analytics challenge problems that require highly advanced computing solutions, collaborative support between RIST, PRACE and XSEDE will enhance the productivity of globally distributed research teams.

(3) Holding technical meetings: Technical meetings will be held to support cross organizational information exchange and collaboration.