Responding to market forces that are driving the otherwise vibrant global electronics industry toward narrower computing applications and away from the next wave of innovation, the Defense Advanced Research Projects Agency (DARPA) is pouring $1.5 billion into “foundational enhancements” designed to jumpstart the post-Moore’s Law electronics industry.

The five-year roadmap dubbed Electronic Resurgence Initiative (ERI) hits the ground running this week with a summit in San Francisco focusing on what program managers identify as ERI’s three pillars: new chip architectures, IC design and materials and integration.

“What we are trying to do are foundational enhancements that are beyond what any one corporate partner would want to do or try to do on their own,” said William Chappell, director of DARPA’s Microsystems Technology Office.

“The double-edged sword of Moore’s Law is that while the train is kept moving, the costs across the board from fab to design to verification have all gone up precipitously and even exponentially,” Chappell added. “What we are trying to do is look at other avenues, for example in fabrication, where you can get benefit through either novel materials or novel integration processes that don’t rely just on the scaling of transistors.”

DARPA also announced a list of university and corporate research efforts aim at advancing its “three-pillar” chip strategy. For example, ERI places a large bet on maintaining U.S. and European leadership in chip design and the valuable intellectual property it generates. “We need to make sure that we have new inventions occurring across our country and other allied countries where we invent new processes as older processes are being replicated en masse.”

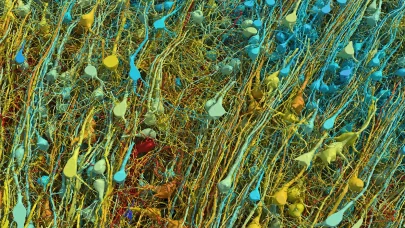

While chip maker Intel Corp. and challengers such as GPU specialist Nvidia Corp. and ARM increasingly focus on specific applications, many driven by AI and other emerging machine learning applications, DARPA is attempting to reboot the semiconductor R&D cycle in response to huge global chip investments. Chappell specifically cited China’s estimated $150 billion investment in an indigenous chip industry. That initiative would underpin broader efforts, including Beijing’s national strategy to become the world leader in AI by 2030.

The technological battleground in this global competition, DARPA reckons, revolves around new materials, automating the design of new systems-on-chips (SoCs) along with novel architectures that could, for example, be mixed and match as building blocks in larger systems. One effort, dubbed Intelligent Design of Electronic Assets, or IDEA, seeks to develop a platform supporting an automated design flow for SoCs along with the chip packages and interconnects to larger systems.

These future chip design flows would leverage machine learning, analytics and automation technologies used to verify chip designs before they are mass produced. Contactors for the IDEA program include Cadence Design Systems, Nvidia and Carnegie Mellon University.

ERI’s chip architecture research focuses on reconfigurable frameworks that leverage specialized hardware to tackle specific computing problems. Contractors for the Software Defined Hardware (SDH) initiative include Intel, Nvidia and top U.S. engineering schools. The hardware effort along with a separate “domain-specific” SoC effort were launched last fall.

Meanwhile, Nvidia will lead a team of industry and university researchers under the SDH program seeking performance gains akin to today’s ASICs “without sacrificing programmability for data-intensive algorithms,” the company said Tuesday (July 24).

Among the goals of chip architecture effort is bringing an open-source software approach to hardware development. Among the applications are machine vison and machine learning, Chappell added.

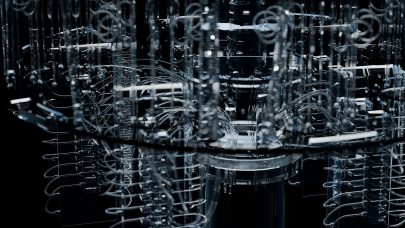

The semiconductor materials and circuit integration theme addresses looming performance issues such as “memory bottlenecks” that plague current big data applications. One task is finding new ways to combine dissimilar blocks of chip intellectual property, many based on different materials and circuit designs. The initiative that includes researchers from MIT, Stanford and other leading engineering schools would focus on both emerging 3-D SoC designs as well as future approaches under the rubric, Foundations for Novel Compute, or FRANC, program.

Among the contractors for the 3-D chip effort is Skywater Technology Foundry, a pure-play 200-mm chip fab in Minnesota with roots dating back to Control Data Corp. and, more recently, Cypress Semiconductor.

Ultimately, DARPA’s Chappell said, the chip initiative is designed “to see what the art of the possible is.”

He added: “It’s more important than ever that we have new inventions coming out of the pipeline to make sure the semiconductor space does not become a commodity.”

–Tiffany Trader, managing editor of HPCwire, contributed to this report.